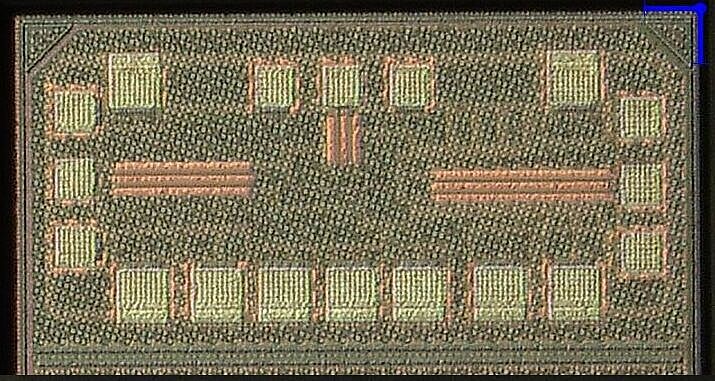

60 Gb/s 1:4 Demultiplexer in 22-nm FD-SOI Technology

Dieser Chip implementiert einen 1:4‑Single‑Ended‑Demultiplexer in binärer Baumstruktur, der für ultraschnelle serielle Datensysteme ausgelegt ist. Er wandelt einen hochratigen seriellen Eingangsdatenstrom in vier parallele Ausgänge um, sodass nachfolgende digitale Schaltungen mit geringeren Taktfrequenzen betrieben werden können. Die Architektur basiert auf einer binären Baumstruktur aus True‑Single‑Phase‑Clock‑(TSPC)‑Flipflops, Latches und einem Frequenzteiler, die alle mit kompakten Gated‑Inverter‑Blöcken realisiert sind. Dieser Designansatz ermöglicht hohe Geschwindigkeiten bei gleichzeitig sehr geringer Schaltungsfläche. Der Demultiplexer unterstützt Eingangsdatentraten von 1,6 Gb/s bis 60 Gb/s und bietet damit einen breiten Einsatzbereich. Die Schaltung kann mit Versorgungsspannungen zwischen 0,6 V und 1,2 V betrieben werden, was flexible Kompromisse zwischen Leistung und Energieverbrauch erlaubt. Gefertigt in 22‑nm‑FD‑SOI‑CMOS‑Technologie, belegt der Chip lediglich 0,033 mm². Der Leistungsverbrauch ist überwiegend dynamisch und skaliert aufgrund der inverterbasierten Architektur naturgemäß mit der Eingangsdatentrate.

Referenz

B. Sadiye, M. Iftekhar, W. Mueller and J. C. Scheytt, "60-Gb/s 1:4 Demultiplexer in 22-nm FD-SOI Technology Using TSPC Logic: A Circuit-to-System-Level Analysis and Design," in IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 34, no. 2, pp. 366-378, Feb. 2026, doi: 10.1109/TVLSI.2025.3625787.