Digital & Mixed Signal Designs

Im Bereich Digital- & Mixed-Signal Designs erforscht die Fachgruppe die Entwurfsautomatisierung von digitalen prozessorbasierten Systemen mit dem Schwerpunkt auf RISC-V-Prozessoren und verschiedenen konfigurierbaren Systems-On-Chip (SoC) Varianten basierend auf Mehrkern-Systemen.

RISC-V steht eine neue Generation von RISC-basierten (Reduced Instruction Set Computer) Prozessoren, welche 2010 als quelloffene und lizenzfreie Befehlssatzarchitektur initiiert wurde und mittlerweile auch für kommerzielle Anwendungen weltweit große Beachtung findet. Seit 2017 betreibt die Fachgruppe Schaltungstechnik im Bereich des Entwurfs digitaler Systeme aktiv eine Ausrichtung auf RISC-V-Prozessoren in Forschung und Lehre.

Die quelloffene freie Verfügbarkeit von RISC-V beschränkt sich nicht nur auf die Dokumentation des Befehlssatzes, sondern umfasst auch auf eine mittlerweile breite Palette von Hardwaremodellen und Entwicklungswerkzeugen. So sind quelloffene Software-Compiler wie g++ und quelloffene Entwurfswerkzeuge wie der Verilator der UC Berkeley verfügbar und man kann verschiedene Varianten quelloffener RISC-V-basierter System-on-Chips (SoC) finden.

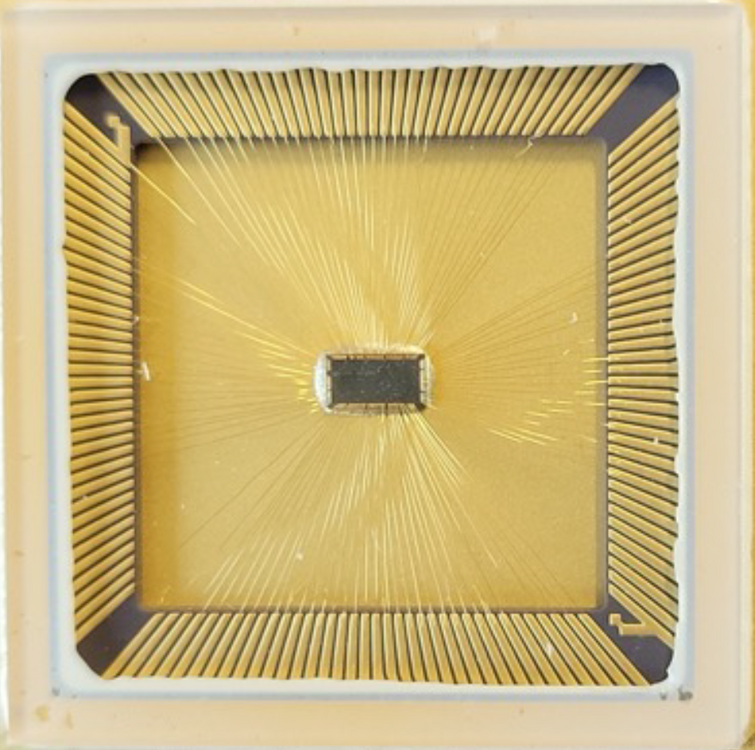

Unsere Arbeiten in diesem Bereich umfassen Entwurfsautomatisierungen sowie Hardware- und Chipentwicklungen auf Basis der Rocket-CPU-Plattform für Mehrkern-Architekturen im Bereich sicherheitskritischer und fehlertoleranter Systeme mit Schwerpunkt auf konfigurierbare und frei skalierbare Lock-Step- und Grid-Varianten mit RISC-V 32-bit-Prozessoren. Entwurfsautomatisierungen basieren auf SystemC und dem Chipyard-Framework mit Arbeiten im Bereich von Hardwarekonfigurationen mit Chisel, RTL-Simulationen mit Verilator, Simulationsbeschleunigungen mit FireSim, FPGA-Synthese mit Vivado und Chipentwürfen mit IHP130, skywater130 und 22FDX-Technologien. Als Entwurfsplattformen dienen konventionelle Workstations und das Noctua2-HPC-Cluster.