Digital & Mixed Signal Designs

RISC-V stands for a new generation of RISC-based (Reduced Instruction Set Computer) processors, which was initiated in 2010 as an open-source and license-free instruction set architecture and is now attracting great attention worldwide for commercial applications. Since 2017, the Circuit Technology group has been actively focusing on RISC-V processors in research and teaching in the field of digital system design.

The open source availability of RISC-V is not just limited to the documentation of the instruction set, but also includes a wide range of hardware models and development tools. Thus, open-source software compilers like g++ and open-source design tools such as UC Berkeley's Verilator became available and one can find several variants of open-source RISC-V-based system-on-chips (SoC).

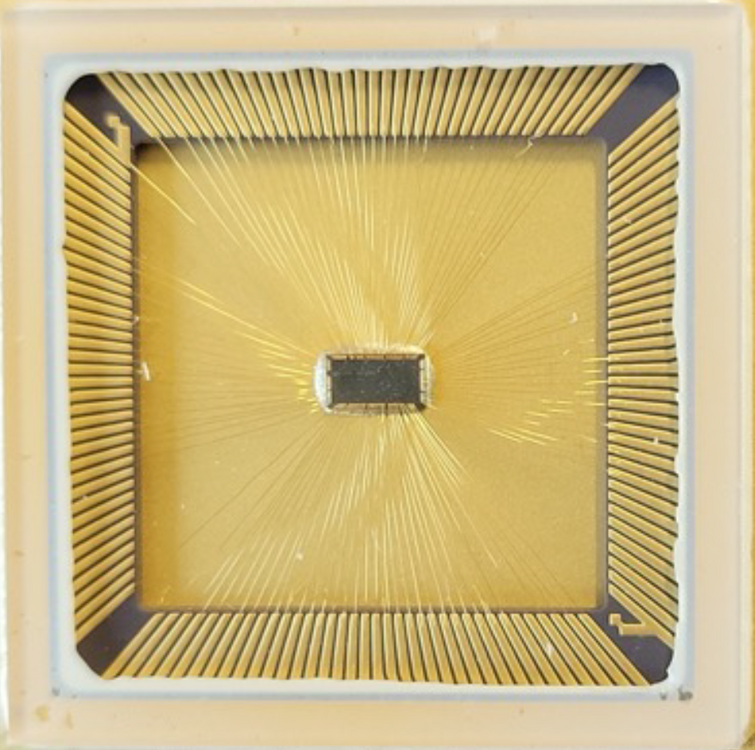

Our work in this area includes electronuc design automation as well as hardware and chip development based on the Rocket CPU platform for multi-core architectures in the area of safety-critical and fault-tolerant systems with a focus on configurable and freely scalable lock-step and grid variants with RISC-V 32-bit processors. Our electronic design automation research is based on SystemC and the Chipyard framework with work in the area of hardware configurations with Chisel, RTL simulations with Verilator, simulation accelerations with FireSim, FPGA synthesis with Vivado and chip designs with IHP130, skywater130 and 22FDX technologies. Conventional workstations and the Noctua2 HPC cluster serve as design platforms.